Silicon Substrate Preparation Process

In this article the details on how a silicon substrate is prepared is given.We have structured the article into 5 sections as give below for easy and effective reading.

2. Electronic grade silicon production

3. Czochralski Crystal Growth Process

If you don’t have a basic idea of IC Fabrication, we have a detailed article on the subject. Visit the link given below.

TAKE A LOOK : IC FABRICATION TECHNIQUES

Silicon Crystal Growth

The most commonly available natural sources of silicon are silica and silicates. At present, silicon-made devices constitute over 95% of all semiconductor devices.

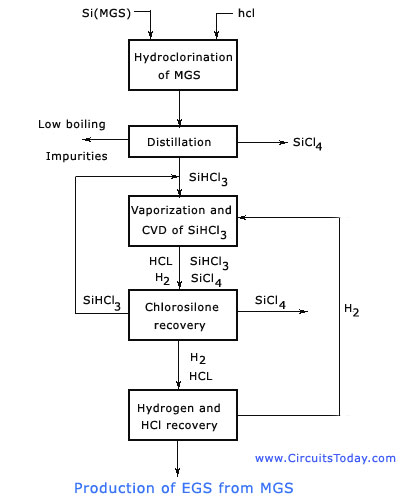

Production of Electronic Grade Silicon (EGS)

Electronic-Grade Silicon (EGS) is the raw material that is used for the preparation of single-crystal silicon. EGS is actually a polycrystalline material of high purity. EGS has some major impurities like boron, carbon, and residual donors. The pure EGS will have doping elements in the parts per billion (ppb) range, and carbon less than 2 parts per million (ppm).

The step by step procedure regarding the production of EGS is shown in the block diagram below.

The process starts by the production of Metallurgical Grade Silicon (MGS) by charging it with quartzite and carbon in an arc furnace. Quartzite is a relatively pure form of sand (SiQ2), and carbon is obtained in the form of coal, coke, and wood chips.

The overall reaction in the furnace is given below.

SiC+Si02 = Si + SiO + CO

The MGS after being drawn off, has to be solidified at a purity of 98%. But this purity is not enough for the manufacture of semiconductor devices. So, the MGS has to be pulverized mechanically and reacted with anhydrous hydrogen chloride (HCI) to form trichlorosilane (SiHCI3). The reaction is shown below.

Si + 3HCl = SiHCI3 + H2

With the help of a catalyst, the reaction takes place at a nominal temperature of 300°C. The reaction creates products like silicon tetrachloride (SiCl4) and the chlorides of impurities. At this point the purification process occurs. The purification process has to be done by fractional distillation method as the products trichlorosilane and unwanted chlorides are liquids at room temperature.

The purified SiHCI3 is subjected to chemical vapor deposition (CVD). The chemical reaction is a hydrogen reduction of SiHCl3.

The chemical reaction is shown below.

2SiHCl3 + 2H2 = 2Si + 6HCl

The reaction takes place in a CVD reactor. A resistance heated Si-rod (4-mm diameter), called a slim-rod, is used as the nucleation point for the deposition of silicon. Through the process rods of EGC are obtained. which are up to 0.2 meters (or more) in diameter and several meters in length. EGS can be cut from these rods as single chunks or crushed into nuggets.

In order to achieve high overall efficiency, a feedback or recycling of reaction of by-products is done. This is also shown in the figure above.

EGS can also be produced by pyrolysis method in which silane (SiH4) will be reacted with heat. The reaction takes place at a high temperature of 900°C. The main advantage of using silane instead of trichlorosilane is the lower production cost and less production of harmful reaction by-products.

SiH4 + HEAT = Si + 2H2

In this process the CVD reactor is operated at about 900°C and supplied with silane instead of trichlorosilane. The advantages of producing EGS from silane are lower cost and less harmful reaction by-products.

Crystal Structure and Growing

As told earlier, the IC components are formed in a single crystal wafer. Though, through the above processes the EGS obtained is highly refined, it is not suitable enough for the manufacturing IC’s. In this section, therefore, we will study the crystal structure and its growing using EGS as raw material.

The silicon wafer, as stated above, must be single crystal, but it does not represent an ideal crystal due to following reasons:

- The wafer has finite boundaries; thus, atoms at the surfaces are incompletely bonded as against those in the bulk of the wafer material.

- The atoms are displaced from their ideal locations by thermal agitation.

Real crystals have defects which are mainly classified into four types:

(1) Point defect

(2) Line defect (dislocation)

(3) Area or planar defect

(4) Volume defect.

The crystal defects influence the optical, electrical, and mechanical properties of silicon.

Point defect refers to following forms of defect:

1. A non-silicon atom is deposited into the lattice at either a substitutional or interstitial site. The former refers to the site produced by replacing a parent silicon atom and the latter refers to the existing site between silicon atoms. The non- silicon atom may be an intentional dopant as introduced by diffusion process (to be discussed) or an unintentional impurity.

2. A vacancy in the lattice created due to missing atom – also known as a Schottky defect.

3. A silicon atom in an interstitial lattice site with an associated vacancy – also known as a Frenkel defect.

Vacancies and interstitials have equilibrium concentrations that depend on temperature. Point defects are important in the kinetics of diffusion and oxidation. The diffusion of many impurities depends on the vacancy concentration, as does the oxidation rate of silicon.

Dislocations form the second class of defects. There may be edge (line) dislocation or screw dislocation. Edge dislocation in a cubic lattice may be created by an extra plane of atoms. Crystals for IC usage are generally grown free of edge dislocations, but may contain small dislocation loops from excess point-defect considerations. These defects act as nuclei for the precipitation of impurities such as oxygen and are responsible for a swirl pattern seen in wafers. Dislocations in devices are generally undesirable, because they act as sinks for metallic impurities and alter diffusion profiles.

4. Chemical vapour deposition (including epitaxy)

5. Metallization

Area defects represent a large area discontinuity in the lattice. The crystal on either side of the discontinuity may be otherwise perfect. Two typical area defects are, twin and grain boundaries. Twinning represents a change in the crystal orientation across a twin plane, such that a certain symmetry, such as mirror image , exists across that plane. In silicon the twin plane is {111}. A grain boundary represents a transition between crystals having no particular orientation relationship to one another. Grain boundaries separate grains of single crystal in polycrystalline silicon. Crystals having such area defects are not used for 1C manufacture.

Precipitates of impurity or dopant atoms constitute the volume defects. Every impurity introduced into the lattice has a solubility; that is, a concentration that the parent lattice can accept in a solid solution of itself and the impurity. If an impurity is introduced (at a temerature T1) at the maximum concentration allowed by its solubility, and the crystal is then cooled to a lower temperature (say T2), a supersaturated condition is said to exist. The crystal achieves an equilibrium state by precipitating the impurity atoms in excess of the solubility level as a second phase which is being a material of different composition and structure. For example, excess metallic impurities can react with silicon and form silicides within the parent lattice. Precipitates are generally undesirable because they act as, sites for dislocation generation.

Crystal Growing

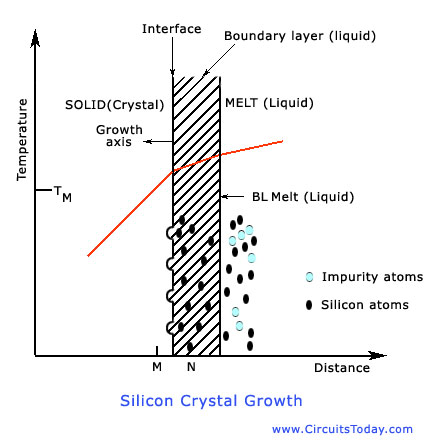

A phase change from solid, liquid, or gas phases or crystalline solid phase occurs in growing crystals. Czochralski growth is the process used to grow most of the crystals from which silicon wafers are produced. The silicon crystal growth is a liquid-solid monocomponent growth system. The growth of a Czochralski (CZ) crystal, to be discussed in the next section, involves the solidification of atoms from a liquid phase at an interface. The speed of the growth is determined by the number of sites on the face of the crystal and the specifics of theheat transfer at the interface. The figure below shows the transport process and temperature gradients involved.

Some of the most important growth parameters of the crystal are the growth rate or growth velocity of the crystal, and the instantaneous solidification rate. We should note that pull rate is the macroscopic indication of net solidification rate. The temperature fluctuations cause a huge difference in the rates near the interface. The growth rate can be greater than or even less than the pull rate at a given time. When the growth rate is lesser than the pull rate, re-melting occurs. Through re-melting, the crystal dissolves back into the melt. This problem has to be solved so as to remove the crystal defects. As a result of this elimination, a more uniformly-doped crystal is formed. The growth rate will surely affect the defect structure and dopant distribution in the crystal on a small scale.

In silicon, every impurity has a solid solubility. The impurity has different equilibrium solubility in the melt. The equilibrium segregation coefficient (ratio of equilibrium castrations in solid to that in liquid) of the impurity or dopant atoms is below unity-this holds good for commonly formed impurities, and commonly used dopants in silicon. Therefore, the impurities at the interface are left in the liquid (melt) during growth. Thus, as the crystal grows, the melt becomes progressively enriched with impurity. The extremely small impurities are incorporated in the grown crystal.

The boundary layer thickness is a function of the convection conditions in the melt (forced convection) produces a boundary layer. In large melts the convection forced by rotation is often secondary to the thermal convection caused by temperature gradients in the crucible. Because the thermal convection is a random process, the thickness of the boundary layer fluctuates with time, resulting in a variable value for boundary layer thickness. The net result of thermal convection effects is an inhomogeneous distribution of dopant in the crystal on a micro scale. The shape of the growing interface is also determined by the pull speed. . Inorder to ensure the stability of the growth process, a proper choice of these conditions is needed.

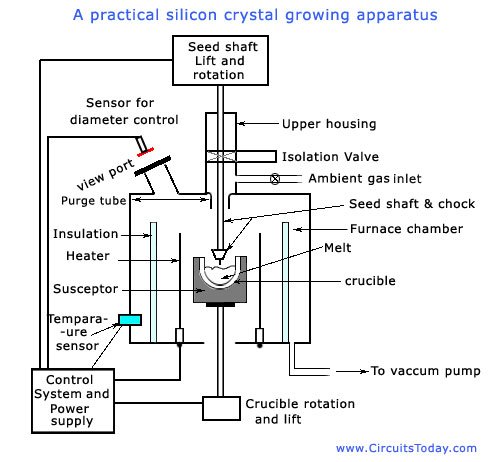

Czochralski Crystal Growth Process

The highly refined silicon (EGS) though free from impurities, is still polycrystalline. Hence it is to be processed to become single crystal. The Czochralski crystal growth process is often used for producing single-crystal silicon ingots. The diagram is given below.

Since monolithic ICs are usually fabricated on a substrate which is doped with impurity, the poly-crystalline silicon with an appropriate amount of dopant is-put into a quartz crucible, which is then placed inside a crystal growth furnace. The material is then heated to a temperature that is slightly in excess of the silicon melting pint of 1420 degree Celsius. A small single-crystal rod of silicon called a seed crystal is then dipped into the silicon melt. The conduction of heat up the seed crystal will produce a reduction in the temperature of the melt in contact with the seed crystal to slightly below the silicon melting point. The silicon will therefore freeze onto the end of the seed crystal, and as the seed crystal is slowly pulled up out of the melt it will pull up with it a solidified mass of silicon that will be a crystallographic continuation of the seed crystal. Both the seed crystal and the crucible are rotated but in opposite directions during the crystal pulling process in order to produce crystalline ingots of circular cross section.

The liquid solid interface remains near to the surface of the melt if the temperature and pulling rate are correctly chosen. Even a long single crystal silicon is pulled from it. The diameter of the ingot is controlled by the pulling rate and the melt temperature, with ingot diameters of about 100 to 150 mm (4 to 6 inches) being the most common. The ingot length will generally be of the order of 3 meter, and several hours are required for the “pulling” of a complete ingot. The crystal pulling is done in an inert-gas atmosphere (usually argon or helium), and sometimes a vacuum is used. This is done to prevent oxidation”

The pull-rate is closely related to the heat input and losses, crystal properties and dimensions. The conditions for crystal pulling are therefore carefully controlled. For example, the melt temperature is monitored with a thermocouple and feedback controller. Longer diameter crystals have commercial advantages and can be grown. However, difficulties may be encountered because of resistivity gradient across finished slices.

The crystal growth apparatus shown in the figure above consists of the following parts.

- Furnace

- Crystal pulling mechanism

- Ambient control facility

- Control system circuitry

The furnace consists of a crucible, susceptor (crucible support) and rotational mechanism, heating element and power supply, and a chamber. As the crucible contains the melt, it is the most important component of the growth apparatus. The crucible material should be chemically unreactive with molten silicon. Also, the material should have high melting point, thermal stability, and hardness. The materials for crucible, which satisfy these properties, are silicon nitride (Si3N4) and fused silica (SiO2). The latter is in exclusive use nowadays. Fused silica; however, reacts with silicon, releasing silicon and oxygen into the melt. In tins process the crucible undergoes erosion. The susceptor, is used to support the silica crucible. It also provides for better thermal conditions. Graphite is the material of choice because of its high-temperature properties. The graphite should be pure to prevent contamination of the crystal from impurities that would be volatilized from the graphite at the temperature involved. The susceptor rests on a pedestal whose shaft is connected to a motor that provides rotation. The whole assembly can usually be raised and lowered to keep the melt level equidistant from a fixed reference point, which is needed for automatic diameter control.

The chamber housing the furnace must provide easy access to the furnace components to facilitate maintenance and cleaning. The furnace structure must be airtight to prevent contamination from the atmosphere, and have a specific design that does not allow any part of the chamber to become so hot that its vapour pressure would be a factor in contaminating the crystal. Hottest parts of the apparatus are water cooled Insulation is usually provided between the heater and the chamber wall.

The crystal-pulling mechanism consists of seed shaft or chain, rotation mechanism, and seed chuck. The mechanism controls two parameters of die growth process: pull rate and crystal rotation. Also, the pulling mechanism must have minimum vibration and great precision. The seed holder and pulling mechanism must maintain precise orientation perpendicular to the melt surface.

From the figure shown below you can see that the crystal leaves the furnace through a purge tube, where ambient gas, if present, is directed along the surface of the crystal to cool it. From the purge tube, the crystal enters an upper chamber, which is usually separated from the furnace by an isolation valve.

The ambient control for the crystal growth apparatus consists of gas source, flow control, purge lube, and exhaust or vacuum system. The crystal growth must be conducted in an inert gas or vacuum as staled earlier. This is necessary because

- The hot graphite parts must be protected from oxygen to prevent erosion and

- The gas around the process should not react with the molten silicon. Growth in vacuum meets these requirements.

Growth in a gaseous atmosphere, generally used on large growers, must use an inert gas such as helium or argon. The inert gas may be at atmospheric pressure or at reduced pressure.

The control system for crystal growing may consist of micro processing sensors, and outputs and provides control of process parameters such as temperature, crystal diameter, pull rate and rotation speed. The use of digital or microprocessor-based systems for control is more common because these rely less on operator intervention and have many parts of the process pre-programmed.

Silicon Wafer Preparation

Ingot Trimming and Slicing

As soon as the crystal ingot is obtained using the above processes, the extreme top and bottom portions of the ingot are cut off and the ingot surface is grounded to produce a constant and exact diameter. The normal diameter is usually 100,125, or 150 mm. A crystallographic orientation flat is also ground along the length of the ingot. The ingot is then sliced using a large-diameter stainless steel saw blade with industrial diamonds embedded into the inner-diameter cutting edge. This will help in producing circular slices or wafers that are about 600 to 1000 micro meters thick. The orientation flat serves as a useful reference plane for various device processes.

Wafer Polishing and Cleaning

When the wafer is sliced, its surface will be heavily damaged. This can be made normal only by polishing. The reasons for polishing are given below.

- To remove the damaged silicon from the sawn surface.

- To produce a highly planar or flat surface that will be required for the photo-lithographic process especially when flue-line geometries are involved.

- To improve the parallel.

The sliced wafer will have saw marks and is 0.6 to 1 mm thick. This is quite rough. Hence it has to be lapped to produce a flat surface. The wafer, before polishing, may have a surface damage in the order of 75 micro meters. Even through lapping, only 60 micro meters can be polished and scraped. The remaining 15 micro meters has to be removed with the help of etching process. The chemical etch consists of an acid mixture, including nitric acid to oxidize the surface and hydrofluoric acid to dissolve the oxide.

The wafer is then made into a mirror like finish by polishing it. This polishing is carried out by using aluminium abrasive powders of decreasing grit size (down to a final 1 micro meters diameter). Even after the polishing, the wafer will still have a surface damage of around 2 micro meters deep. This is removed by an additional chemical etching stage, which can sometimes be simultaneous with the final polishing stage.

In most cases, only one side of the wafer s carefully polished to produce a mirror like image. The other side is given a normal lapping procedure to provide a somewhat flat surface with agreeable parallelism. After the wafer polishing operations are completed, the wafers are thoroughly cleaned, and dried, and they are now ready to be used for the various processing steps described in the following sections. Before discussing these steps let us discuss some processing considerations necessary to maintain the purity and perfection of the material.

Wafer Processing Considerations

1. Chemical Cleaning

The wafers are cleaned thoroughly as soon as the polishing is completed. Originally, the silicon wafers are cleaned so as to remove all organic films, heavy metals, and particulars:. The commonly used cleaning agents are aqueous mixtures of NH4OH – H2O2, HCI – H2O2, and,H2SO4 – H2O2.

All of the above solutions are good enough in removing metallic impurities, but, out of the lot, the HCI – H2O2, mixture is the best

2. Gettering Treatments

The transition group elements which act as the metallic impurities are located at the interstitial or substitutional lattice sites and act as generation-recombination centres for the carriers. The precipitated forms of these impurities are usually silicides. These silicides are known to be electrically conductive . In the case of VLSI circuits, these transition group elements decrease their performance, especially in the case of dynamic random access memories and narrow-base bipolar transistors, as they are sensitive to conductive impurity precipitates.

Normally, a process called gettering treatment is carried out to remove the impurities. Gettering is a process that removes,and harms the impurities or defects them from the regions in a wafer where devices are fabricated. Pregettering refers to a gettering treatment provided to silicon wafers that are used for IC processing. When the wafer with sinks are developed for device processing, the impurities are absorbed with the help of pregettering process. The common techniques that are used for gettering treatment are given below:

- Common mechanical abrasion methods like lapping and sand blasting are carried out to damage the back surface of the wafer.

- A focused heat beam from a Q-pulsed, Nd-YAG laser is used to damage the wafer. Dislocations are made in the wafer by rastering the laser beam along the wafer’s back surface. Thus they become favorable trapping sites for fast-diffusing species.

- Intrinsic gettering – As told earlier, when an impurity oxygen precipitates, defects are generated. The defects generated by oxygen precipitation are useful as trapping sites. As the wafer is needed for device fabrication, high temperature cycle is employed to lower the oxygen content near the surface of the wafer. Additional thermal cycles are added to promote the formation of oxygen precipitates and defects in the interior of the wafer.

The different IC fabrication techniques that come after Silicon Substrate Preparation are explained below.

- Chemical Vapour Deposition (CVD)

- Oxidation Process in IC Fabrication

- Photolithography

- Diffusion of Impurities for IC Fabrication

- Ion Implantation

- Metallization Process

Comments are closed.