Dielectric Isolation in Integrated Circuits

This article focuses on Dielectric isolation in various Integrated Circuits; especially in the VLSI sector, discusses various methods used for dielectric isolation like V-groove isolation, Silicon on Insulator technology and Epitaxial layer overgrowth.

Dielectric isolation, as you all know, is the process of electrically isolating various components in the IC chip from the substrate and from each other by an insulating layer. It’s main use is to eliminate undesirable parasitic junction capacitance or leakage currents associated with certain applications.

The various methods of dielectric isolation are:

V-Groove Isolation

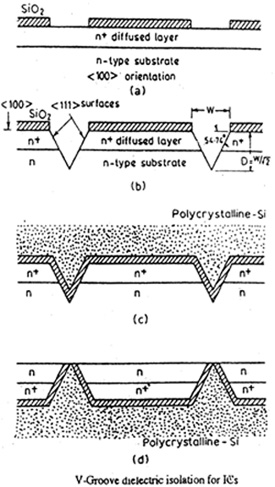

V-groove isolation is formed with an n-type substrate, on which an n+ diffusion is performed. As a next step an SiO2 layer is formed, which is then patterned to form a grid of intersecting lines opening in the oxide. V-groove isolation process is shown in the figure below.

The wafer formed is then exposed to an orientation dependent etching (ODE) process, where the patterned layer is used as the etching mask; which results in the formation of V-shaped grooves as shown in the picture (b). In this the <111> plane sidewalls are at an angle of 54.74 degree with respect to the <100> top surface of the silicon wafer.

As a result the starting material is <111> oriented crystal, which is normally used for p-n junction isolation. But for dielectric isolation the starting material is <100> oriental silicon.The etchant used in the above step etches away the exposed silicon anisotropically, this means that the etch rate is much faster along the <111> planes than along the <100> crystal planes. This kind of preferential etching is the key reason behind the formation of V-groove. The depth D of the isolation groove can be determined in the initial oxide cut width W as

D = W/√2

Next step is covering the sidewalls of the V-groove with an oxide layer, therefore the wafer is subjected to a thermal oxidation process. After completing the oxide layer, a very thick layer of polycrystalline silicon is deposited as shown in picture (c).

The most critical step in the V-groove isolation process is explained in figure (d). Keeping polycrystalline surface side of the wafer down, silicon wafers are mounted on the lapping plate. In the next step, n-type silicon substrate is then carefully lapped down to the level at which the vertices of the V-grooves become exposed.So now we get an array of n-type single crystal silicon regions that are isolated from the polycrystalline silicon substrate. Polycrystalline silicon now serves to provide the mechanical support for the IC.This material is ideal for the function because of its good thermal expansion coefficient, it can withstand high processing temperatures, and is a good match to single crystal silicon.

The n-type silicon has now moved down to vertices of the V-grooves because of the lapping operation. If the lapping is recessive, then proper isolation will not be achieved.But if excessive lapping is done, it may lead to thinner n-type regions. Wafer diameter is approx 100mm and the V-groove depth is about 10 micro meters, thus precise lapping is necessary.

The n+ diffused layer serves as a buried layer to reduce the collector series resistance of the n-p-n transistors The rest of the processing sequence for the dialectically isolated ICs follows along the same line as for the conventional junction isolated IC.

The dielectric isolation is useful for such applications as high-voltage and radiation-resistant ICs. This isolation technique is much more expensive than junction isolation technique because it requires extra processing steps.

Advantage of dielectric isolation:

Excess free electrons and holes created in the silicon as a result of high energy ionisation by photo radiation causes a large increase in the leakage current of the pn junctions in the IC; which obviously is undesirable and can cause damage.The dielectric isolation in the IC is resistant and protects the IC from such large transients.

Below listed are some reasons for the reduced parasitic capacitance:

- Permittivity of SiO2 is one reason, which is 1/3rd of Silicon and hence capacitance is reduced.

- Oxide is thicker than the depletion region of the substrate junction and capacitance is inversely proportional to the thickness of oxide.

- No need of applying negetive potential to the substrate.

Silicon-on-lnsulator Technology

It’s another process for creating dielectrically isolated devices. In this process, a thin layer of single-crystal silicon can be produced on top of a thermal SiO2 layer on a silicon wafer. Strips of oxide are produced by patterning the oxide layer using photolithography. As a next step, a thin layer of silicon is then deposited on the wafer.It will be polycrystalline in the regions where the deposited silicon layer overlays the oxide and it will be single crystal in the regions where there is direct contact with silicon substrate. In the next step we will directionally recrystalise the silicon layer, which inturn recrystallises the substrate to act as the nucleation centre.As the heated zone is scanned across the wafer the crystal growth, propagates from these nucleation regions to the regions of the silicon film on top of the oxide islands or strips.Thus we form a complete single crystal layer of silicon.

Epitaxial Lateral Overgrowth (ELO)

The Epitaxial Lateral Overgrowth (ELO) is related to Silicon on Insulator process.Like in SOI process, the starting material is thermally oxidised silicon wafer in which the oxide layer is patterned to islands or stripes using photolithographic techniques.Next step is a repeated sequence of carefully controlled CVD silicon deposition, followed vapour phase etching cycles to produce single crystal silicon film on the silicon substrate.

A preferential removal of polycrystalline silicon (deposited on top of SiO2) happens during the vapour phase etching process.In the next steps,as successive cycles of the CVD deposition and vapour-phase etching process continues,the single-crystal silicon that is formed in the oxide windows starts to extend over the adjoining oxide regions,and at the same time any polycrystalline silicon that is deposited on top of the oxide is removed by the vapour-phase etching process.As a result a complete single crystal layer of silicon is formed.

8 Comments

Thanks.. It is a great source of knowledge for me .

yah…….good topic…thanks….